端午节假期宅在家中闲来无事,翻出了《编码》这本书。里面偏软件的内容我略过没看,但是偏向硬件的真是解答了我的很多疑惑。

逻辑门

高中应该是数学课上学过简单的逻辑运算,那个时候就曾疑惑过,逻辑门凭什么可以在输出端为0的情况下输出端为1?是怎样的黑魔法可以在断开的情况下还能让灯泡亮呢?这个疑惑就如同发现永动机,明知不对还不得不相信就是这样。当时老师给的答案一如既往的简洁,规定就是这样。这个答案是正确的,逻辑上的确如此,可是我更像知道现实中是如何做到这看似不可能的事情,而这本书告诉了我真实的实现方式。

继电器

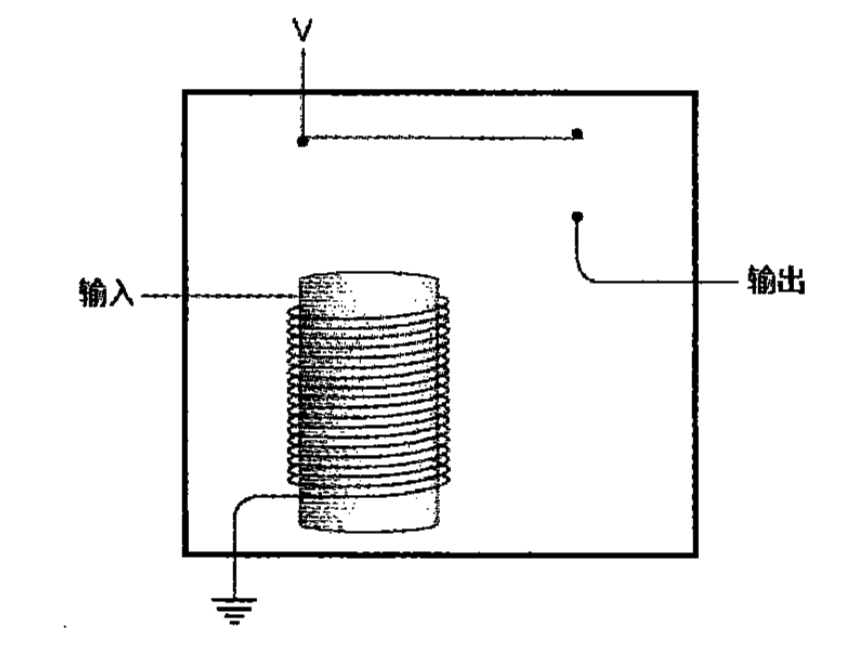

下图是一个简单的继电器,合上开关产生吸力于是让电路联通。

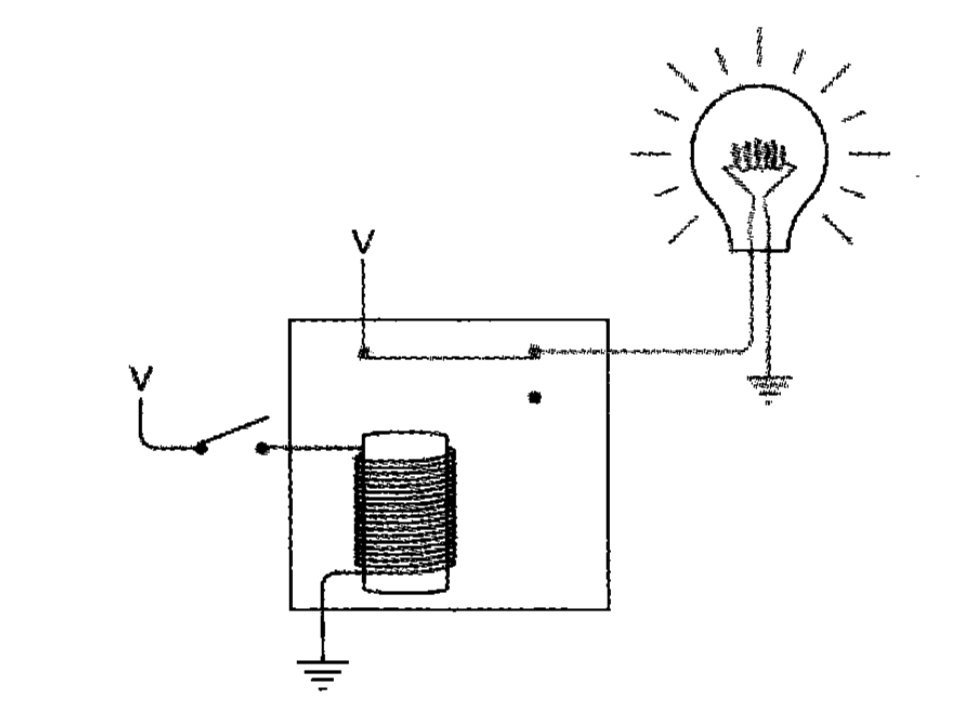

而第二幅图通过改造一下联通电路,从而做到关闭开关时候,没有吸力从而让电路联通。

也就是说输出端的高电压并非从开关电路来的,因而做到了断开电路依然灯泡会亮。原来看到结果后觉得如此的简单,但是在知道这一切之前却怎么也想不明白。

加法器

加法器更多是逻辑上的表示,并没有太多问题。明白逻辑门之后跟上理解透彻。但是其中多个一致的小单元组成大单元,这样的思想却会贯穿所有功能的实现。

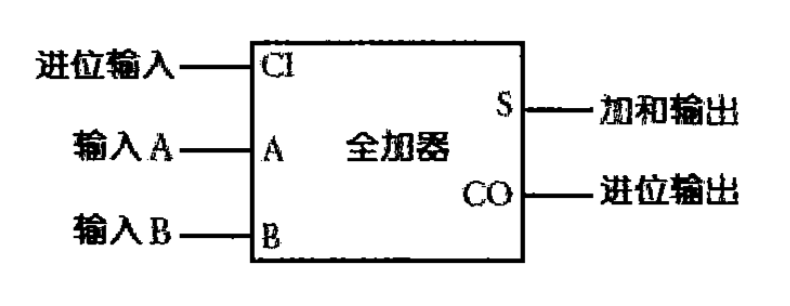

全加器

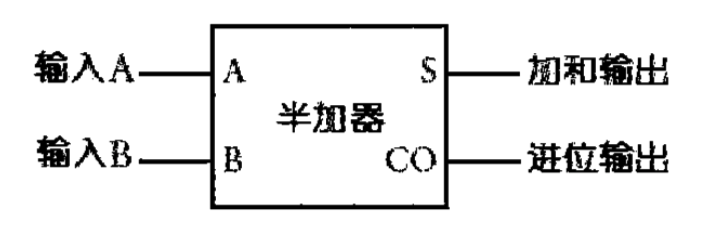

两个输入端,两个输出端。输出端分别表示当前位的结果和是否有进位符。

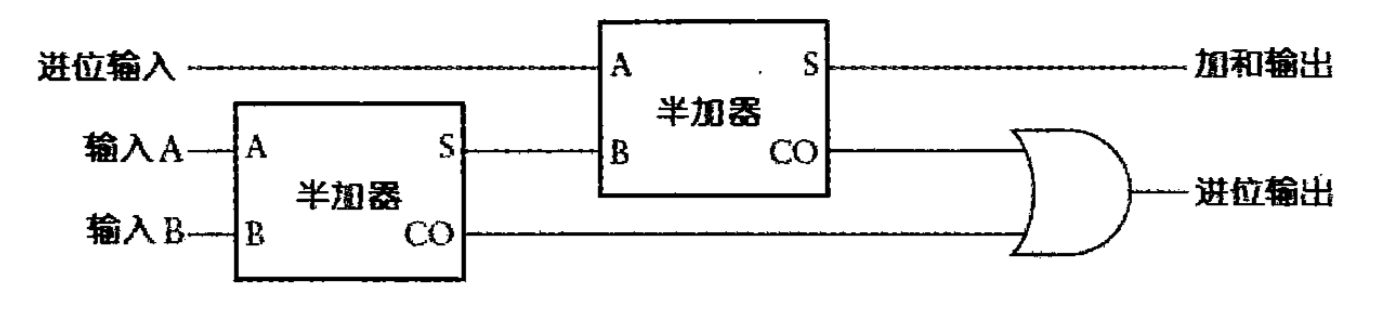

但是这只是半加器,为什么叫半加器呢?因为完整是加法单元还需要将进位计算在内。 完整的加法单元如下。

用下图简化表示

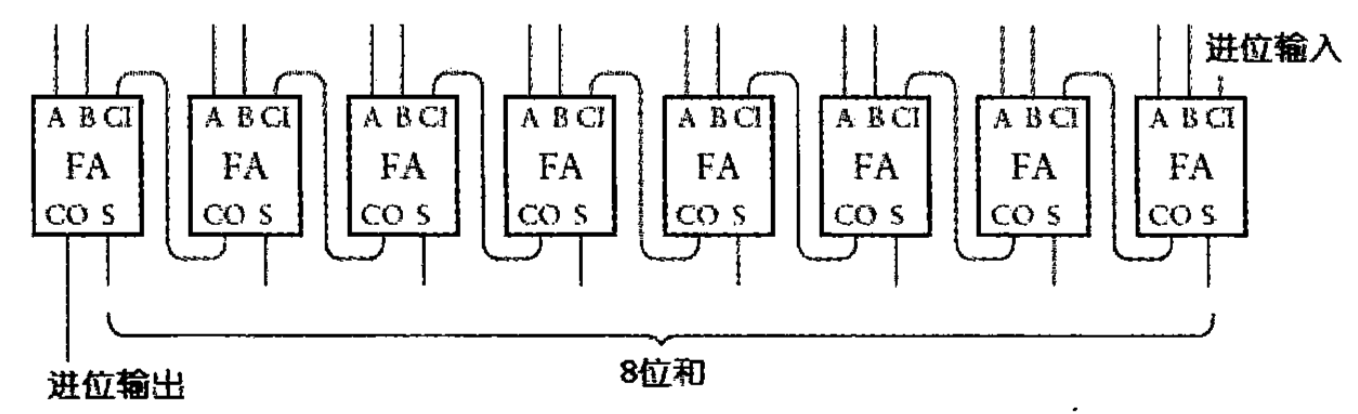

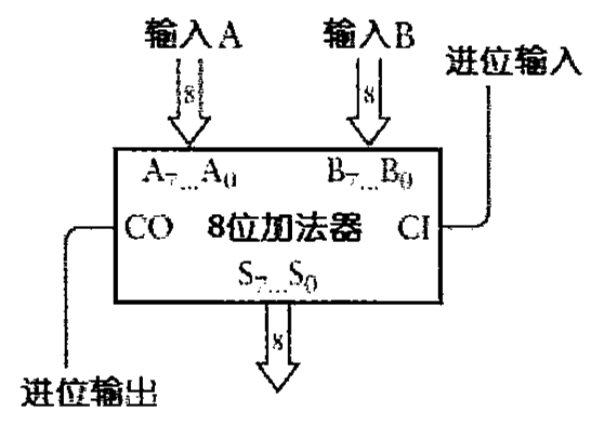

8位加法器

有了一位的全加器,就可以组成一个8位的加法器。具体实现如下

简化表示如下图

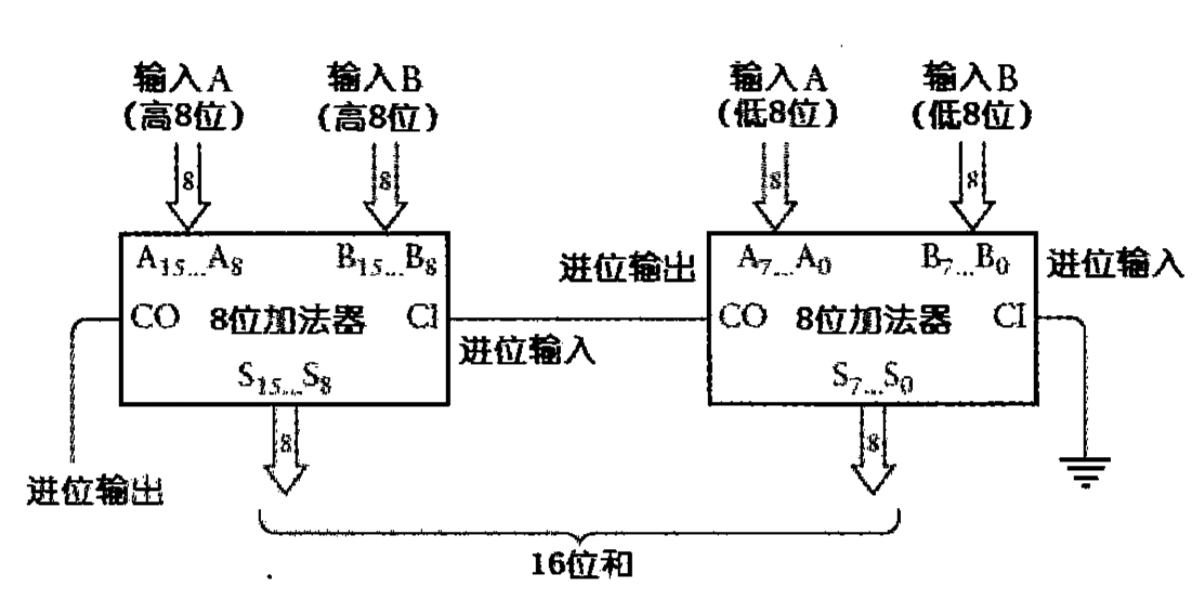

N位加法器

从1位加法器组成8位后,我们便可以通过8位组成一个16位的,进而逻辑上获得N位的加法器

内存

通过”多个一致的小单元组成大单元“这一思想,可以得到一个4GB的内存必然也是有许多1byte的单元组成。

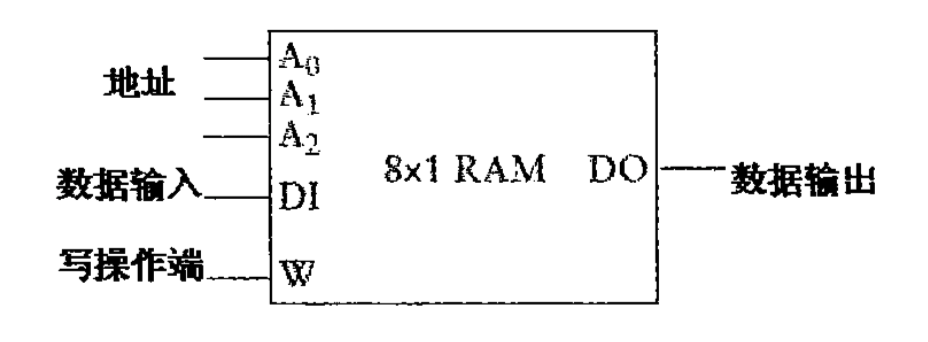

1byte内存

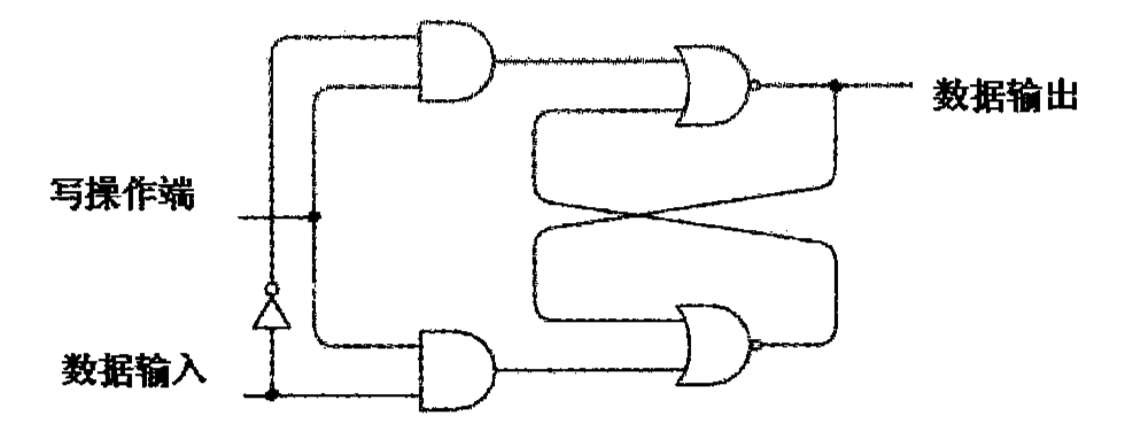

下图中的电路有以下特性

- 写操作端输入为1,数据输出与数据输入一致。

- 写操作端输入为0,数据输出与不受数据端影响,并且维持在输入端最后的状态。

根据上述特性,可以发现数据输出端储存了输入端的数据了。 因此这就是一个简单的1byte内存,称为位锁存器。

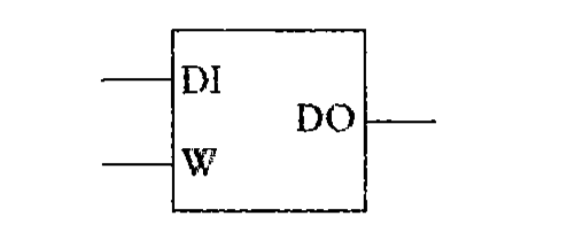

简化图如下

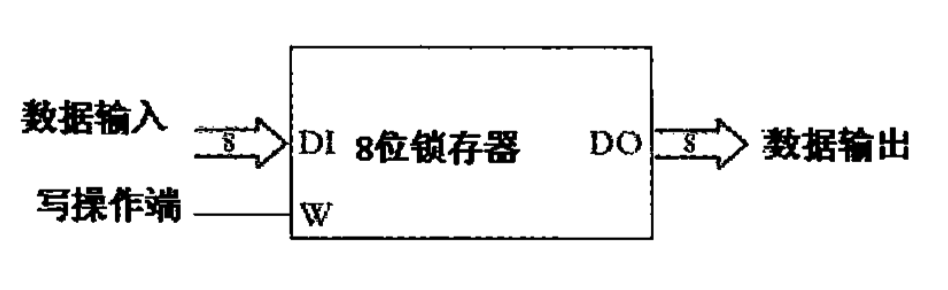

8byte内存

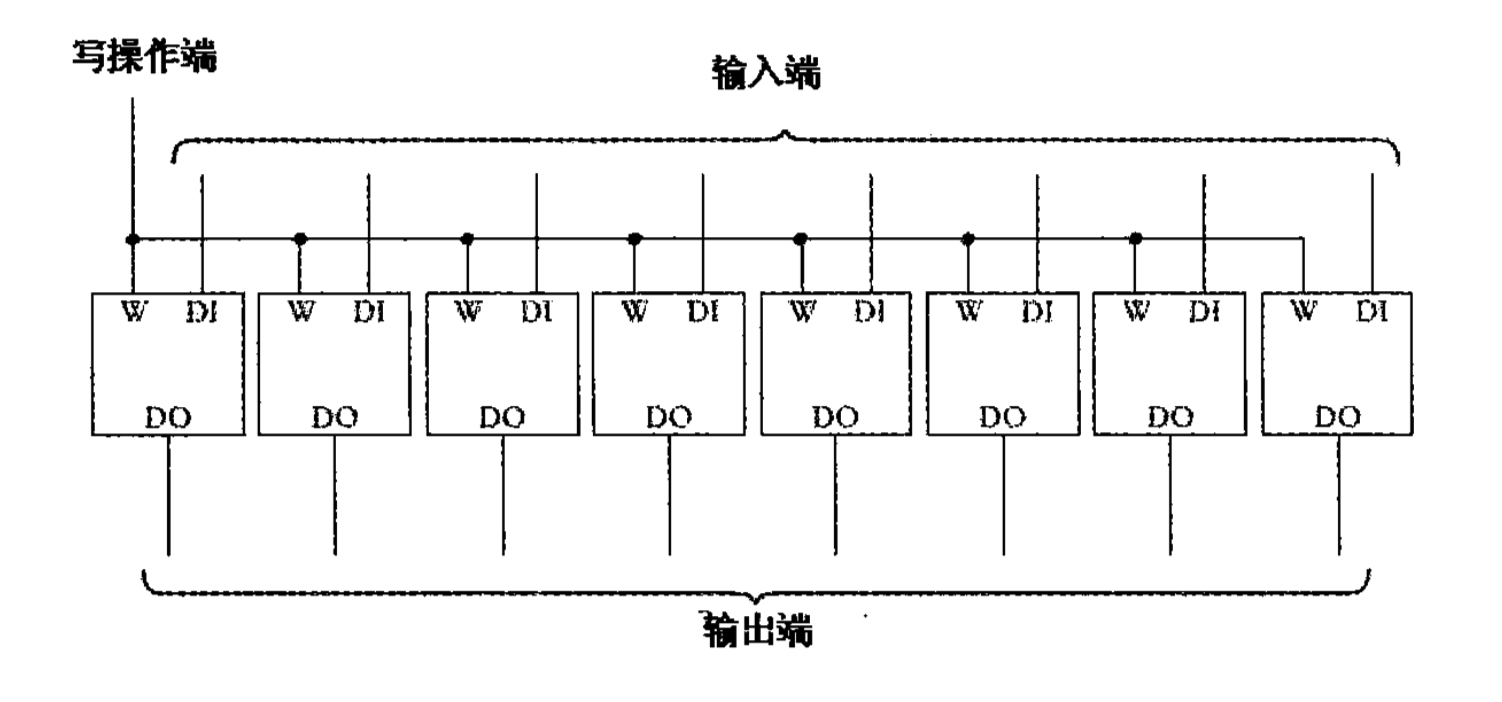

位锁存器简单的组合我们就可以得到一个8位的内存

简化图如下

8byte内存进阶

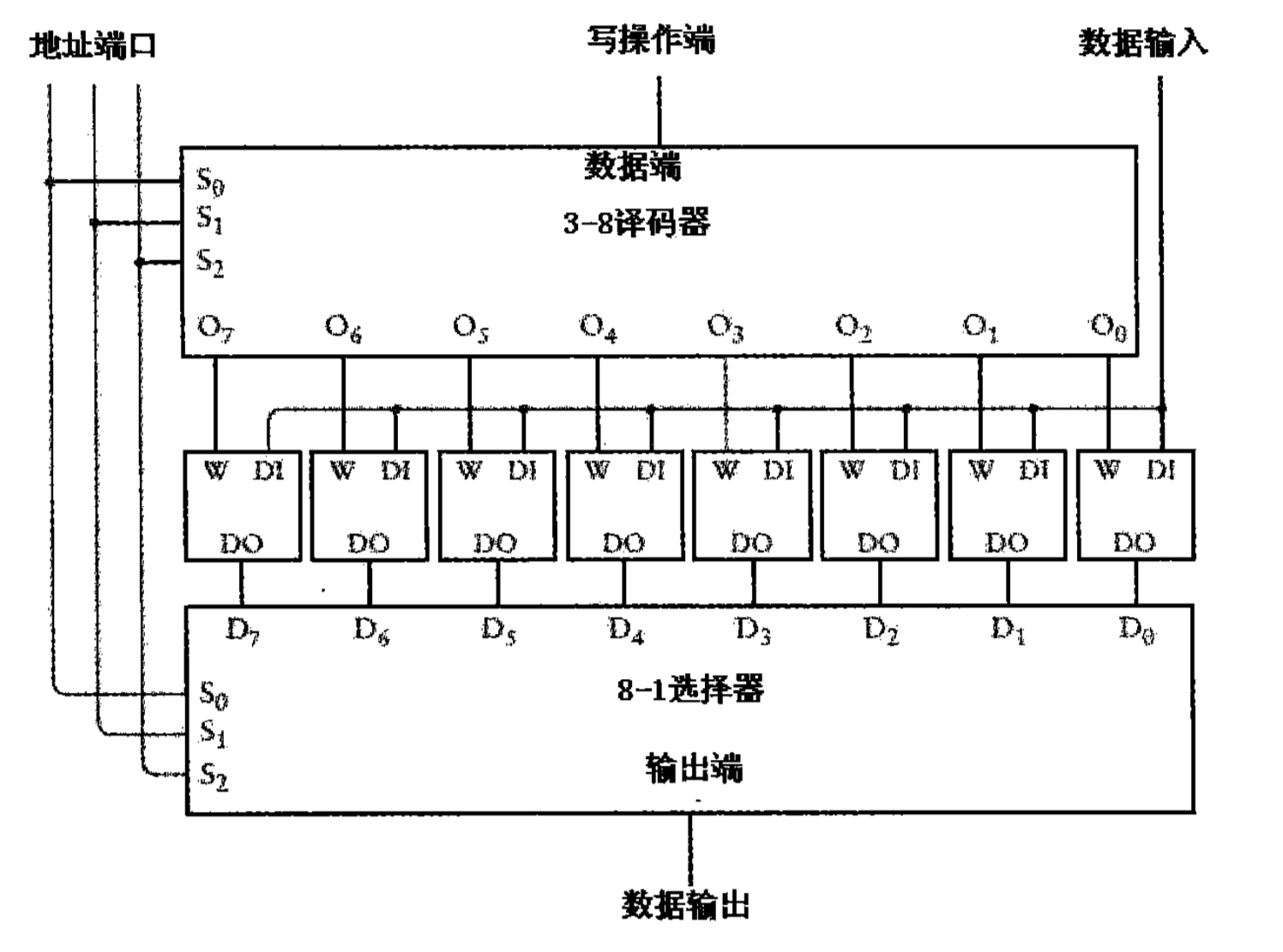

8byte内存有个问题,输入输出都是8位,如此扩展下去岂不是4GB内存输入输出也都得4GB了。我们希望的是指定输入某个位置,指定某个位置作为输出。因此做了一些改动

在输入端和输出端分别增加译码器和选择器。而其中的关键改变在于增加了地址,这也是内存中常说的32位和64位。对于一个8byte的内存,我们只需要3位地址即可表示8byte的空间。 简化表示如下

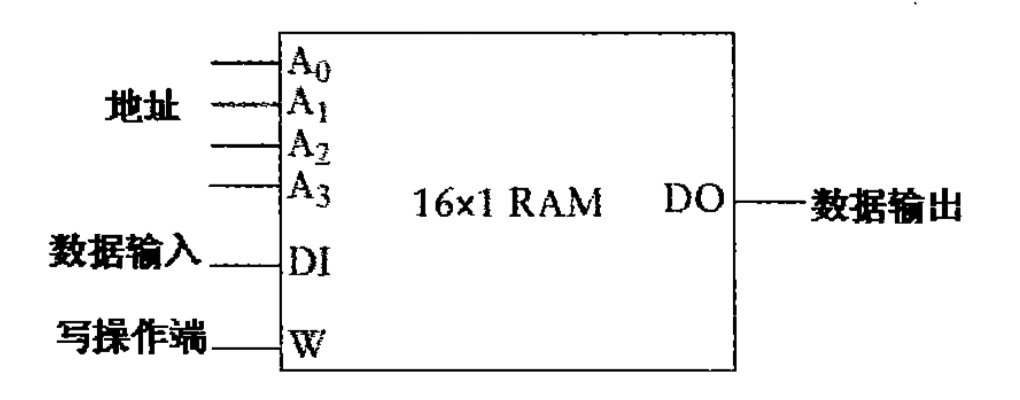

16byte内存

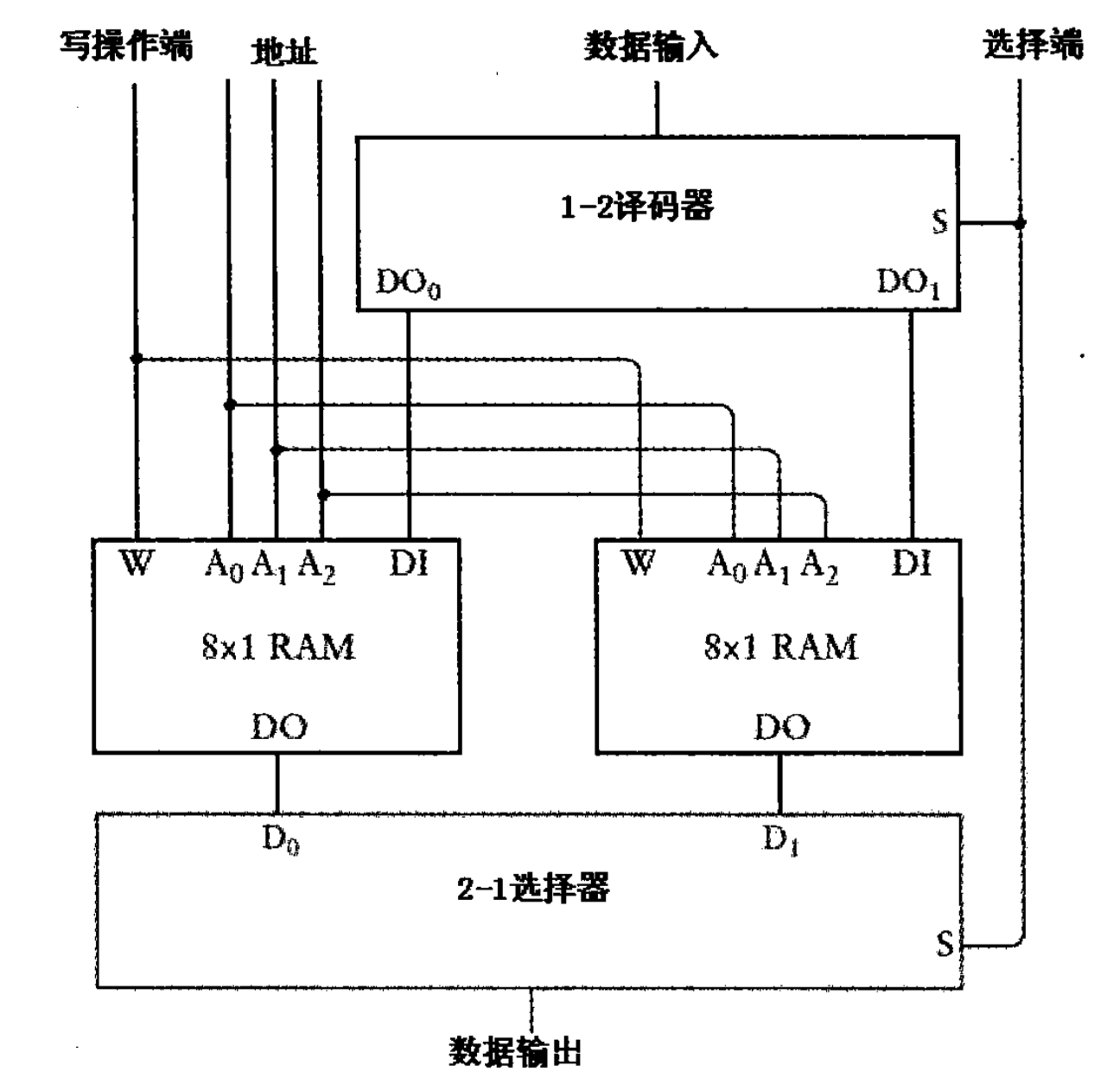

依然通过8byte内存组成一个16byte的内存。实现如下图

这里两个8byte内存并不是简单连接,而是其中多了一个选择端。选择端是用来选择2个8byte内存中的一个。我们可以将其认为是8byte内存单元的地址,和1byte的地址等价。因此简化图如下

如此一来N byte的内存也就不难实现

译码器

译码器这部分书中并未提到,但是也是困扰过我的。很难现象一个个指令如何成为一个个行为的。但是根据书中的基本知识我大概能够想到指令的实现过程。因此下面这些是我个人的理解,可能存在错误。

- 译码器的输出交给控制器,而控制器连接着运算单元和存储单元等组件。

- 一个指令对于一个二进制码,可以认为是译码器的地址,寻址到不同的输出,例如3线-8线译码器或4线-16线译码器。

- 这样译码器的输出控制着运算和存储的进行。

形象说来译码器像是控制着各个单元的开关一样,这些开关告诉控制器改如何联通各个单元,以及如何读取读取写入数据。